## RECONFIGURABLE COMPUTING

(work in progress)

Gheorghe M. Ştefan

This document was prepared with LATEX  $2_{\ensuremath{\mathcal{E}}}\! X \, 2_{\ensuremath{\mathcal{E}}}\! X$

## Introduction

Anyone can build a fast CPU. The trick is to build a fast system.

Seymour Cray (1925-1996)

The concept of reconfigurable computing, RC, has existed since the 1960s, when Gerald Estrin's paper [Estrin '60] proposed the concept of a computer made of a standard processor and an array of "reconfigurable" hardware. The main processor would control the behavior of the reconfigurable hardware.

RC emerges as a solution to two main shortcomings suffered by the computing systems that originated in the 1940s:

**Turing tariff**: Turing-based universal computer could perform any function, but not necessarily efficiently. The flexibility of Turing-based computers can still be used for complex computation, while for intense computation acceleration solutions will have to be found.

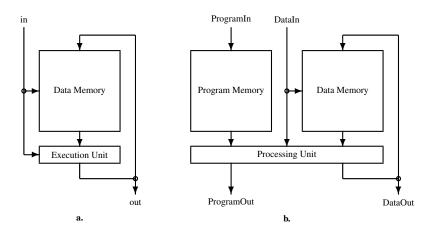

von Neumann bottleneck: the abstract model of computation disseminated by John von Neumann, in his 1945 report, provides a solution with a *small and complex processor* connected to a *simple and big memory* through a communication channel which isolates data and programs from the engine which work on data according to programs. The *Harvard abstract model*, issued in the same time, relaxes a little the limitation but the main problem remains: data are isolated from the processing engine.

The emergence of the SRAM-based field-programmable gate array (FPGA) in the 1980s boosted Reconfigurable Computing as a research and engineering field.

The book is structured in eight chapters organized in three parts followed by three appendixes.

**First part**: **PRELIMINARIES**, introduces the theoretical and historical context in which reconfigurable computation appears and will develop.

**First chapter**: *History*, answers, from a historical perspective, the question: why reconfigurable computing?

**Second chapter** Why do we need reconfigurable computation?, describes the current spectrum of possibilities offered by computer science.

**Third chapter**: *System-level Organization for Reconfigurable Computation*, provide a general description of a reconfigurable computing system.

**Fourth chapter**: *Mathematical Models of Computation*, is a short review of the main mathematical models of computation involved in defining what the reconfigurable computation could be.

- **Second part**: **DIGITAL HIERARCHY**, is a review of the hardware resources we have to use circuits as a computability model.

- **Fifth chapter**: *Digital System Hierarchy*, describes the circuits that can be used to design the accelerator part of the reconfigurable computing system. It starts with combinational circuits and ends with mono-core programmable computing systems.

- **Sixth chapter**: *Cellular System Hierarchy*, deals with the hierarchy of cellular systems starting with cellular automata and describes various systems improved functionally by adding global loops.

- **Seventh chapter**: *Recursive Hierarchy*, introduces an abstract model for parallel computing based on the Stephen Kleene's partial recursive functions model.

- **Third part**: *RECONFIGURABLE SYSTEMS*, provides the main techniques involved in supporting the implementation of RC systems.

- **Eight chapter**: *Optimizing Reconfigurable Systems*, deals with the optimization of the way the code must be written iin order to optimize the hardware of the accelerator.

- **Ninth chapter**: *Optimizing Pseudo-reconfigurable Systems*, provides an efficient solution for designing the functionality of the accelerator.

- **APPENDIXES Composition: the only independent rule in Kleene's model**: the proof that out of three rules in the partial recursive model, only the first, the composition, is independent, the other two can be expressed as a composition of specific compositions.

- **How to instantiate DSP48E1**: provide the Verilog code used to instantiate the DSP48E1 module.

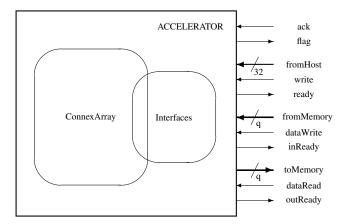

- **ConnexArray**<sup>TM</sup> **simulator**: provides the full description of the simulator for the generic ConnexArray<sup>TM</sup> used as accelerator for the pseudo-reconfigurable version proposed in the last capitol of this book.

What do we expect in the post-Moore era? Improvements in computing performance will come from technologies at the "Top" of the computing hierarchy, not from those at the basic technological level (transistors). Thus we will assist to the reversing of the historical trend.

In the hardware field, processor simplification and domain specialization are expected to add performance in the near future.

It is important to specify what means processor *simplification*! We will define carefully what means *simple* (see Subsection 2.4.2).

And in terms of specialization, we will highlight several levels at which it can be applied. From this perspective, we will distinguish between reconfigurable and pseudo-reconfigurable computation.

## **Contents**

| I | PR   | ELIMINARIES                                                      | 1  |

|---|------|------------------------------------------------------------------|----|

| 1 | Hist | tory                                                             | 3  |

| _ | 1.1  | Imaginary history                                                | 3  |

|   | 1.2  | Conceptual history                                               | 5  |

|   | 1.3  | Factual history                                                  | 9  |

|   | 1.4  | Merged history                                                   | 11 |

|   | 1.5  | User-driven evolution: Computation as General-Purpose Technology | 14 |

|   | 1.6  | Application-driven history                                       | 15 |

|   | 1.7  | Programming paradigms                                            | 17 |

|   | 1.8  | The Qubit                                                        | 18 |

| 2 | Why  | y do we need reconfigurable computation?                         | 19 |

|   | 2.1  | Mono-core approach                                               | 19 |

|   | 2.2  | Multi-core approach                                              | 21 |

|   | 2.3  | Many-core approach                                               | 21 |

|   | 2.4  | Complexity vs. Size                                              | 21 |

|   | 2.5  | Communication vs. computation                                    | 23 |

|   | 2.6  | Host & Accelerator                                               | 23 |

|   | 2.7  | High-level language vs. library of functions                     | 23 |

|   | 2.8  | Turing tariff                                                    | 23 |

| 3 | Syst | tem-level organization                                           | 27 |

|   | 3.1  | Defining reconfigurable computing                                | 27 |

|   | 3.2  | Taxonomy                                                         | 27 |

| 4 | Mat  | thematical Models of Computation                                 | 31 |

|   | 4.1  | Circuits                                                         | 31 |

|   | 4.2  | Turing/Post Model                                                | 37 |

|   | 4.3  | Church Model                                                     | 39 |

|   | 4.4  | Kleene Model                                                     | 40 |

| 5 | Desi | igning Reconfigurable Systems                                    | 43 |

|   | 5.1  | High Level Synthesis                                             | 43 |

|   | 5.2  | Examples                                                         | 53 |

|   | 5.3  | Programming Reconfigurable Systems                               | 69 |

6 CONTENTS

| II  | DIGITAL HIERARCHY                                                                                                                                                                                                                                                                                                                                                                   | <b>71</b>              |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 6   | Digital System Hierarchy         6.1 Combinational Circuits: Zero-order Digital Systems          6.2 Memory Circuits: First-order Digital Systems          6.3 Automata Circuits: Second-order Digital Systems          6.4 Processing Circuits: Third-order Digital Systems          6.5 Computing Circuits: Fourth-order Digital Systems          6.6 Enhanced Computing Circuits | 92<br>99<br>105<br>124 |

| 7   | Cellular System Hierarchy         7.1       Cellular Automata: Nth-order Digital Systems                                                                                                                                                                                                                                                                                            | 153                    |

| 8   | Recursive Hierarchy         8.1 Integrating ConnexArray <sup>TM</sup> as Accelerator in a Computing System         8.2 ACCELERATOR as a Recursive Structured Parallel Engine         8.3 Programming Recursive Structured Parallel Engine                                                                                                                                           | 170                    |

| II  | I RECONFIGURABLE SYSTEMS                                                                                                                                                                                                                                                                                                                                                            | 175                    |

| 9   | Designing Pseudo-Reconfigurable Systems         9.1 The Pseudo-Reconfigurable Computing System                                                                                                                                                                                                                                                                                      |                        |

| Aj  | ppendixes                                                                                                                                                                                                                                                                                                                                                                           | 186                    |

| A   | Composition: the only independent rule in Kleene's model  A.1 Preliminary Definitions                                                                                                                                                                                                                                                                                               | 192<br>193             |

| В   | How to instantiate DSP48E1                                                                                                                                                                                                                                                                                                                                                          | 195                    |

| C   | ConnexArray <sup>TM</sup> Simulator  C.1 Top Module: simulator.v                                                                                                                                                                                                                                                                                                                    |                        |

| Bil | ibliography                                                                                                                                                                                                                                                                                                                                                                         | 221                    |

## **Contents (detailed)**

| I | PR   | ELIM  | INARIES                                                               |  |

|---|------|-------|-----------------------------------------------------------------------|--|

| 1 | Hist | ory   |                                                                       |  |

|   | 1.1  |       | nary history                                                          |  |

|   |      | 1.1.1 | Antiquity                                                             |  |

|   |      |       | Hephaestus & Vulcan                                                   |  |

|   |      |       | Pygmalion                                                             |  |

|   |      | 1.1.2 | Middle Ages                                                           |  |

|   |      |       | Golem                                                                 |  |

|   |      |       | Artificial animals and creatures at the court of Emperor Frederick II |  |

|   |      |       | Brazen Head                                                           |  |

|   |      |       | Homunculus                                                            |  |

|   |      | 1.1.3 | Modernity                                                             |  |

|   |      |       | Frankenstein's Creature                                               |  |

|   |      |       | Offenbach's Olympia                                                   |  |

|   |      |       | Karel Capek's Robota                                                  |  |

|   |      |       | Fritz Lang's Metropolis                                               |  |

|   |      | 1.1.4 | Contemporary                                                          |  |

|   | 1.2  | Conce | ptual history                                                         |  |

|   |      | 1.2.1 | Binary Arithmetic to the Chinese                                      |  |

|   |      | 1.2.2 | Epimenides of Crete                                                   |  |

|   |      | 1.2.3 | Liar's paradox in Middle Ages                                         |  |

|   |      |       | Boethius                                                              |  |

|   |      |       | Peter Abelard                                                         |  |

|   |      |       | William of Ockham                                                     |  |

|   |      | 1.2.4 | Gottfried Wilhelm von Leibniz                                         |  |

|   |      |       | Binary representation                                                 |  |

|   |      |       | Calculus ratiocinator                                                 |  |

|   |      | 1.2.5 | George Boole                                                          |  |

|   |      | 1.2.6 | 1900-1928: David Hilbert                                              |  |

|   |      | 1.2.7 | 1931: Kurt Gödel                                                      |  |

|   |      | 1.2.8 | 1936: Church – Kleene – Post – Turing                                 |  |

|   |      |       | Alonzo Church                                                         |  |

|   |      |       | Stephen Kleene                                                        |  |

|   |      |       | Emil Post                                                             |  |

|   |      |       | Alan Turing                                                           |  |

|   |      | 1.2.9 | 1940s: abstract models of computation                                 |  |

|   |      |       | 1943: Neural nets                                                     |  |

|   |      |       | 1944: Harvard abstract model                                          |  |

|   |     | 1945: von Neumann abstract model                                 |

|---|-----|------------------------------------------------------------------|

|   | 1.3 | Factual history                                                  |

|   |     | 1.3.1 Antikythera mechanism                                      |

|   |     | 1.3.2 Hero of Alexandria                                         |

|   |     | 1.3.3 Gerbert of Aurillac                                        |

|   |     | 1.3.4 Wilhelm Schickard                                          |

|   |     | 1.3.5 Blaise Pascal                                              |

|   |     | 1.3.6 Gottfried Wilhelm von Leibniz                              |

|   |     | 1.3.7 Joseph Marie Charles <i>dit</i> Jacquard                   |

|   |     | 1.3.8 Charles Babbage                                            |

|   |     | Difference engine                                                |

|   |     | Analytical Engine                                                |

|   |     | 1.3.9 Ada Byron, Countess of Lovelace                            |

|   |     | 1.3.10 Herman Hollerith                                          |

|   |     | 1.3.11 Claude Shannon & Thomas Flowers                           |

|   |     |                                                                  |

|   |     | Implementing electro-mechanically Boolean functions              |

|   | 1.4 | Implementing electronically Boolean functions                    |

|   | 1.4 | Merged history                                                   |

|   |     | 1.4.1 Colossus                                                   |

|   |     | 1.4.2 ENIAC – EDVAC                                              |

|   |     | ENIAC                                                            |

|   |     | EDVAC                                                            |

|   |     | 1.4.3 Princeton computer                                         |

|   |     | 1.4.4 IBM entered the scene                                      |

|   |     | 1.4.5 John Backus: first involvement                             |

|   |     | 1.4.6 Computer architecture                                      |

|   |     | 1.4.7 John Backus: second involvement                            |

|   |     | 1.4.8 Parallel computing enter the scene on the back door        |

|   |     | 1.4.9 RISC                                                       |

|   |     | 1.4.10 FPGA & Adaptive Computer Acceleration Platform            |

|   | 1.5 | User-driven evolution: Computation as General-Purpose Technology |

|   |     | 1.5.1 Microsoft's Surface                                        |

|   |     | 1.5.2 Google's Tensor Processing Unit                            |

|   |     | 1.5.3 Apple's M1                                                 |

|   |     | 1.5.4 Tesla's Artificial Intelligence & Autopilot                |

|   |     | 1.5.5 Hadoop & Big-Data                                          |

|   |     | 1.5.6 The Next Target: Artificial General Intelligence           |

|   | 1.6 | Application-driven history                                       |

|   | 1.7 | Programming paradigms                                            |

|   | 1.8 | The Qubit                                                        |

|   |     |                                                                  |

| 2 | Why | do we need reconfigurable computation?                           |

|   | 2.1 | Mono-core approach                                               |

|   |     | 2.1.1 CISC                                                       |

|   |     | 2.1.2 RISC                                                       |

|   |     | 2.1.3 Memory wall                                                |

|   | 2.2 | Multi-core approach                                              |

|   | 2.3 | Many-core approach                                               |

|   |     | 2.3.1 Heterogenous approach                                      |

|   |     | 2.3.2 Adaptive Compute Acceleration Platform (ACAP)              |

|   |     |                                                                  |

|   |      | 2.3.3 Accelerator-Level Parallelism                                |

|---|------|--------------------------------------------------------------------|

|   | 2.4  | Complexity vs. Size                                                |

|   | 2.7  | 2.4.1 Circuit size vs. circuit complexity                          |

|   |      | 2.4.2 Complex computation vs. intense computation                  |

|   | 2.5  | Communication vs. computation                                      |

|   | 2.6  | Host & Accelerator                                                 |

|   | 2.7  | High-level language vs. library of functions                       |

|   | 2.7  | Turing tariff                                                      |

|   | 2.0  | Turing tarin                                                       |

| 3 | Syst | rem-level organization 27                                          |

|   | 3.1  | Defining reconfigurable computing                                  |

|   | 3.2  | Taxonomy                                                           |

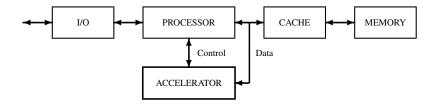

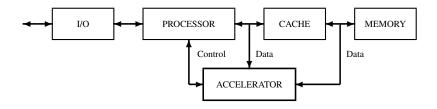

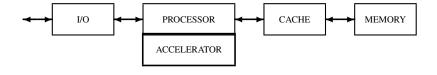

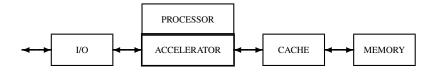

|   | 3.2  | 3.2.1 Heterogenous accelerated computing                           |

|   |      | Stand-alone accelerator                                            |

|   |      | Attached processing unit                                           |

|   |      | 1 0                                                                |

|   |      | •                                                                  |

|   |      | Tightly coupled co-processor                                       |

|   |      | Flexible coupled accelerator                                       |

|   |      | Accelerator embedded in processor                                  |

|   |      | Processor embedded in accelerator                                  |

|   |      | 3.2.2 Reconfigurable accelerators                                  |

| 4 | Mad  | hometical Madala of Commutation                                    |

| 4 |      | chematical Models of Computation 31                                |

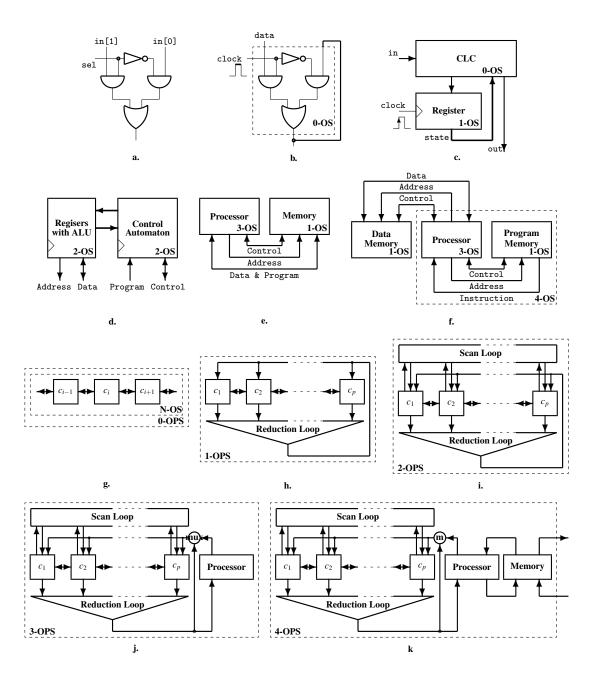

|   | 4.1  | Circuits                                                           |

|   |      | Uniform/nonuniform circuits                                        |

|   |      | Logic circuits                                                     |

|   |      | 4.1.1 Combinational circuits                                       |

|   |      | 4.1.2 Pipelined circuits                                           |

|   |      | 4.1.3 Iterative circuits                                           |

|   |      | 4.1.4 Controlled circuits                                          |

|   | 4.2  | Turing/Post Model                                                  |

|   |      | 4.2.1 The Halting Problem                                          |

|   | 4.3  | Church Model                                                       |

|   |      | 4.3.1 The Halting Problem                                          |

|   | 4.4  | Kleene Model                                                       |

|   |      | 4.4.1 The Halting Problem                                          |

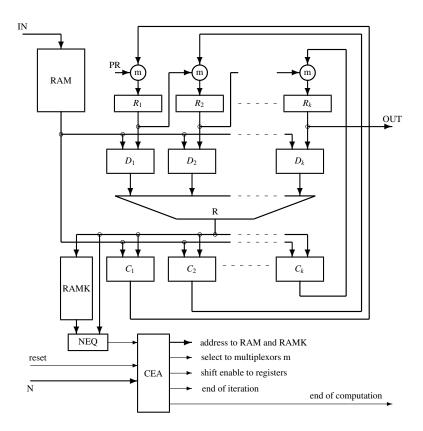

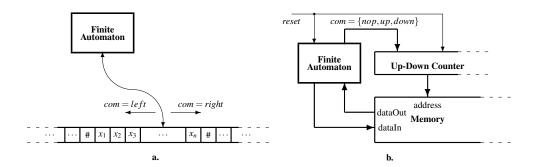

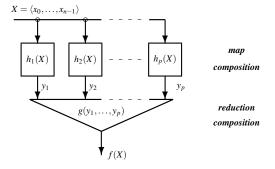

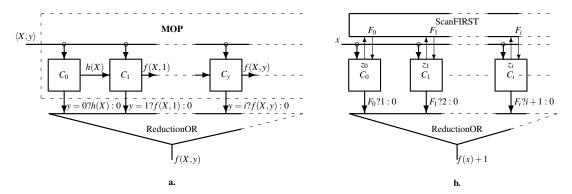

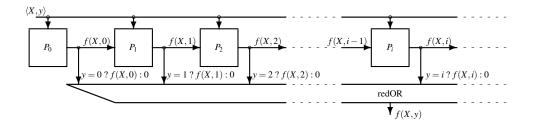

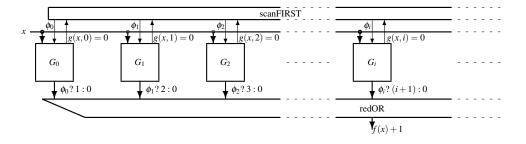

|   |      | 4.4.2 The Circuit Implementation of Partial Recursive Functions 41 |

|   |      | The circuit for the composition rule                               |

|   |      | The circuit for the primitive recursion rule                       |

|   |      | The circuit for the minimisation rule                              |

|   |      | The chesic for the minimisation rate                               |

| 5 | Desi | igning Reconfigurable Systems 43                                   |

|   | 5.1  | High Level Synthesis                                               |

|   |      | 5.1.1 Organization                                                 |

|   |      | 5.1.2 Processing Rate                                              |

|   |      | Managing resource limitations                                      |

|   |      | Managing recurrences                                               |

|   |      | 5.1.3 Coding style issues                                          |

|   | 5.2  | •                                                                  |

|   | 5.2  | Examples                                                           |

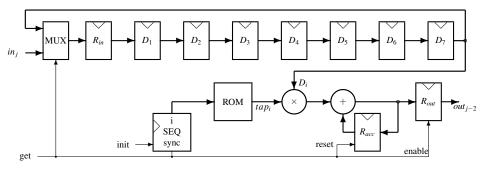

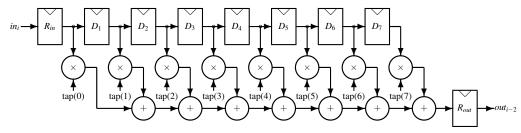

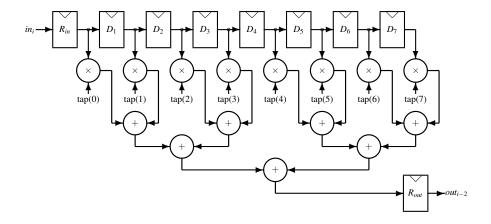

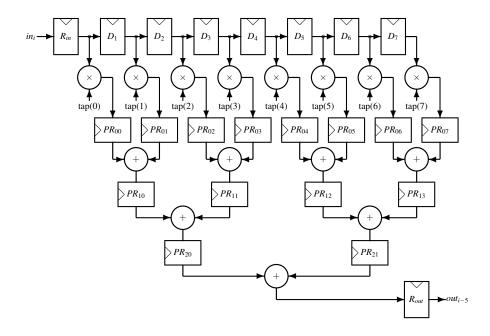

|   |      | 5.2.1 FIR 53                                                       |

|    |            |          | Preliminaries about speed                               | 54       |

|----|------------|----------|---------------------------------------------------------|----------|

|    |            |          | Clock period & circuit structure                        | 55       |

|    |            |          |                                                         | 55       |

|    |            |          | Loop splitting                                          | 55       |

|    |            |          |                                                         | 56       |

|    |            |          |                                                         | 57       |

|    |            |          |                                                         | 57       |

|    |            |          |                                                         | 58       |

|    |            |          | 7 1 71                                                  | 58       |

|    |            |          |                                                         | 58       |

|    |            | 5.2.2    |                                                         | 61       |

|    |            | 3.2.2    | 1                                                       | 61       |

|    |            |          |                                                         | 62       |

|    |            | 5.2.3    | J 1 &                                                   | 63       |

|    |            | 5.2.4    |                                                         | 63       |

|    |            | 5.2.5    | 1                                                       | 63       |

|    |            | 3.2.3    | 1                                                       | 63       |

|    |            |          |                                                         | 65       |

|    |            | 506      |                                                         |          |

|    | <i>5</i> 2 | 5.2.6    | E                                                       | 69       |

|    | 5.3        | Progra   | mming Reconfigurable Systems                            | 69       |

| II | DI         | GITA     | L HIERARCHY 7                                           | 71       |

| 6  | Digi       | tal Syst | em Hierarchy                                            | 73       |

|    | 6.1        | Combi    | national Circuits: Zero-order Digital Systems           | 76       |

|    |            | 6.1.1    | Behavioral vs. structural                               | 76       |

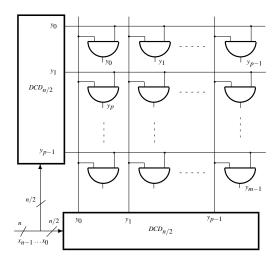

|    |            |          | DCD                                                     | 76       |

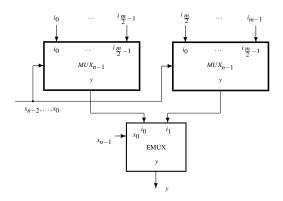

|    |            |          | MUX                                                     | 76       |

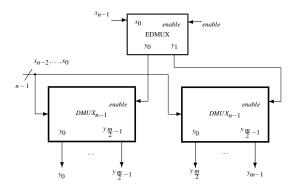

|    |            |          | DMUX                                                    | 77       |

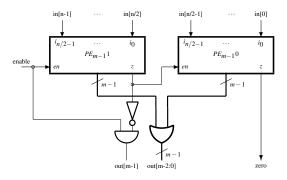

|    |            |          | PE                                                      | 77       |

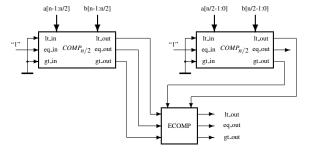

|    |            |          | COMP                                                    | 78       |

|    |            |          | PREFIX                                                  | 78       |

|    |            |          | CSA                                                     | 78       |

|    |            |          | Four-input <i>n</i> -bit adder with ripple-carry adders | 78       |

|    |            |          |                                                         | 79       |

|    |            | 6.1.2    |                                                         | 80       |

|    |            |          |                                                         | 80       |

|    |            |          |                                                         | 81       |

|    |            |          |                                                         | 82       |

|    |            |          |                                                         | 82       |

|    |            |          |                                                         | 83       |

|    |            |          |                                                         | 84       |

|    |            |          |                                                         | 88       |

|    |            |          |                                                         | 88       |

|    |            |          |                                                         | 91       |

|    | 6.2        | Memor    |                                                         | 91<br>92 |

|    | 0.2        | 6.2.1    |                                                         | 92<br>92 |

|    |            | 0.2.1    |                                                         | 92<br>92 |

|    |            |          | · ·                                                     | 92<br>92 |

|    |            |          |                                                         |          |

|     |        | BRAM (Block SRAM in FPGA)                               | 93  |

|-----|--------|---------------------------------------------------------|-----|

|     | 6.2.2  | Register Files                                          | 94  |

|     | 6.2.3  | Pipelining                                              | 94  |

|     |        | REDUCE                                                  | 94  |

|     |        | PERMUTE                                                 | 96  |

|     |        | SYSTOLIC MATRIX-VECTOR MULTIPLIER                       | 98  |

| 6.3 | Auton  | nata Circuits: Second-order Digital Systems             | 99  |

|     | 6.3.1  | Function-oriented automata: the simple automata         |     |

|     |        | RALU (Register file with ALU)                           | 99  |

|     |        | Informational structure & information                   |     |

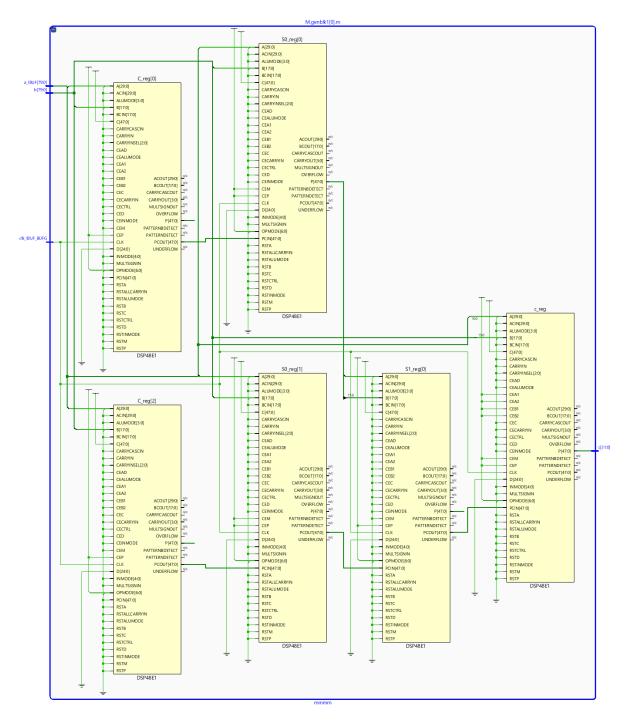

|     |        | DSP (Digital Signal Processing module in FPGA)          | 102 |

|     | 6.3.2  | Finite automata: the complex automata                   | 102 |

|     |        | Generators                                              | 102 |

|     |        | Recognizers                                             | 103 |

|     |        | Control automata                                        | 104 |

| 6.4 | Proces | ssing Circuits: Third-order Digital Systems             | 105 |

|     | 6.4.1  | Counter extended automata (CEA)                         | 105 |

|     | 6.4.2  | Push-down automata                                      | 107 |

|     | 6.4.3  | Processor                                               | 109 |

|     |        | Processor & information: generic definition             | 109 |

|     |        | Elementary processor                                    | 109 |

|     |        | CISC vs. RISC                                           | 109 |

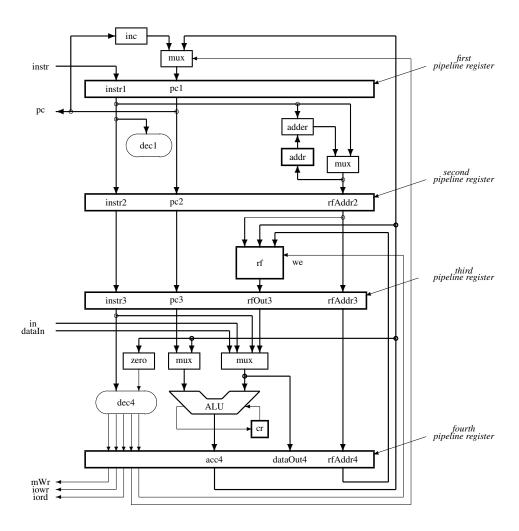

|     |        | Accumulator-based processor                             |     |

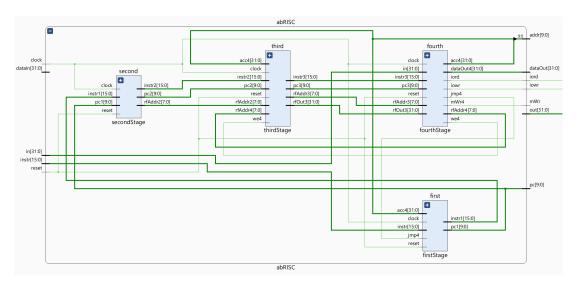

|     |        | The simulation environment for abRISC                   | 119 |

| 6.5 | Comp   | uting Circuits: Fourth-order Digital Systems            | 124 |

|     | 6.5.1  | von Neumann abstract machine                            | 124 |

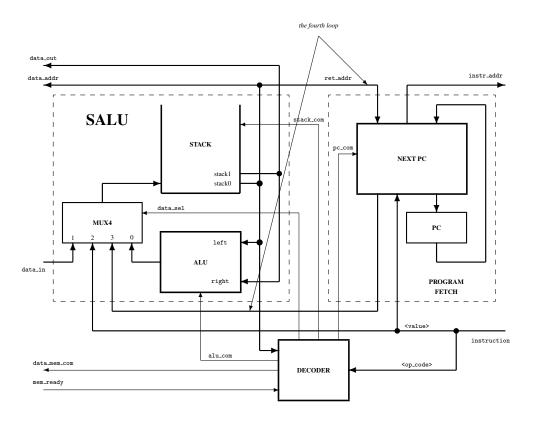

|     | 6.5.2  | The stack processor – a processor as 4-OS               |     |

|     |        | The organization                                        | 125 |

|     |        | The micro-architecture                                  | 128 |

|     |        | The instruction set architecture                        | 131 |

|     |        | Implementation: from micro-architecture to architecture | 131 |

|     |        | Instruction nop                                         | 133 |

|     |        | Instruction add                                         | 133 |

|     |        | Instruction load                                        |     |

|     |        | Instruction inc                                         |     |

|     |        | Instruction store                                       |     |

|     |        | Instruction push                                        | 135 |

|     |        | Instruction dup                                         | 135 |

|     |        | Instruction over                                        | 135 |

|     |        | Instruction zero                                        | 136 |

|     |        | Instruction jmp                                         |     |

|     |        | Instruction call                                        |     |

|     |        | Instruction cjmpz                                       |     |

|     |        | Instruction ret                                         |     |

|     |        | Time performances                                       |     |

|     |        | Concluding about our Stack Processor                    |     |

| 6.6 |        | nced Computing Circuits                                 |     |

|     | 6.6.1  | Harvard abstract machine                                | 138 |

| 7          | Cell                  | ular System Hierarchy                                                           | 139 |  |  |  |  |

|------------|-----------------------|---------------------------------------------------------------------------------|-----|--|--|--|--|

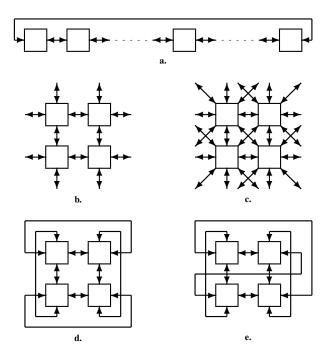

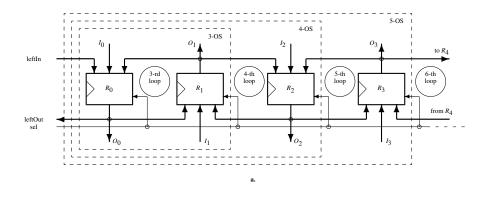

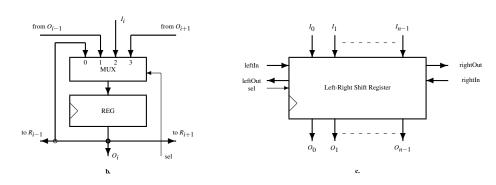

|            | 7.1                   | Cellular Automata: Nth-order Digital Systems                                    | 139 |  |  |  |  |

|            |                       | 7.1.1 General definitions                                                       |     |  |  |  |  |

|            |                       | The linear cellular automaton                                                   | 139 |  |  |  |  |

|            |                       | The two-dimension cellular automaton                                            |     |  |  |  |  |

|            |                       | 7.1.2 Functional CA                                                             |     |  |  |  |  |

|            |                       | Left-Right Shift Register                                                       |     |  |  |  |  |

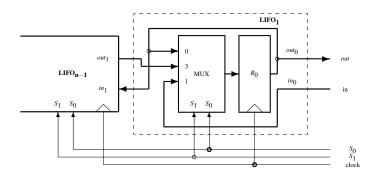

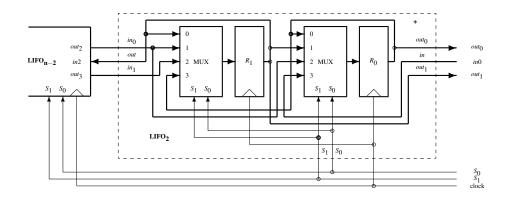

|            |                       | LIFO                                                                            |     |  |  |  |  |

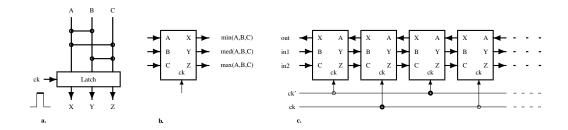

|            |                       | SYSTOLIC SORTER                                                                 |     |  |  |  |  |

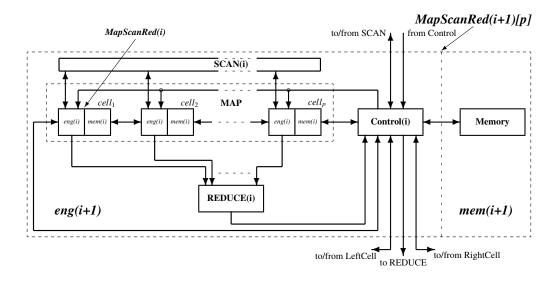

|            | 7.2                   | The First Global Loop: Generic Connex Array $^{TM}$                             |     |  |  |  |  |

|            | 7.2                   | 7.2.1 The behavioral description of Generic ConnexArray <sup>TM</sup>           |     |  |  |  |  |

|            |                       | The Instruction Set Architecture                                                |     |  |  |  |  |

|            |                       | Program Control Section                                                         |     |  |  |  |  |

|            |                       | Operand selection in controller                                                 |     |  |  |  |  |

|            |                       | Data operations in controller                                                   |     |  |  |  |  |

|            |                       | •                                                                               |     |  |  |  |  |

|            |                       | Spatial control in array                                                        |     |  |  |  |  |

|            |                       | Operand selection in the array's cells                                          |     |  |  |  |  |

|            |                       | Data operations in the array's cells                                            |     |  |  |  |  |

|            |                       | Vector transfer                                                                 |     |  |  |  |  |

|            |                       | 7.2.2 Assembler Programming the Generic Connex Array <sup><math>TM</math></sup> |     |  |  |  |  |

|            | 7.3                   | The Second Global Loop: Search Oriented Generic Connex Array $^{TM}$            | 163 |  |  |  |  |

| 8          | Recursive Hierarchy 1 |                                                                                 |     |  |  |  |  |

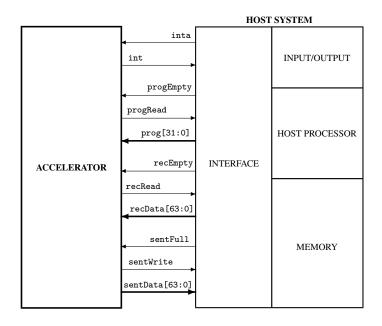

| Ü          | 8.1                   | Integrating Connex Array $^{TM}$ as Accelerator in a Computing System           |     |  |  |  |  |

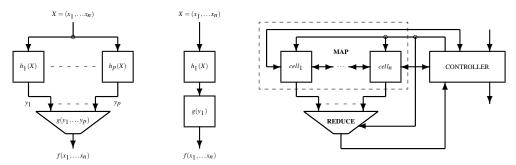

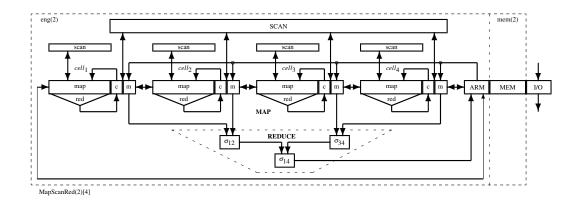

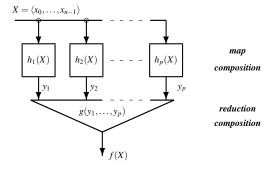

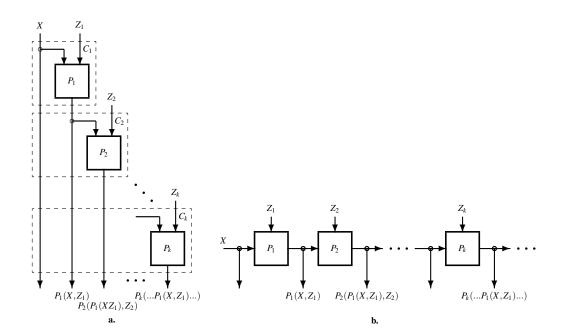

|            | 8.2                   | ACCELERATOR as a Recursive Structured Parallel Engine                           |     |  |  |  |  |

|            | 8.3                   | Programming Recursive Structured Parallel Engine                                |     |  |  |  |  |

|            | 0.5                   | Trogramming Recursive Structured Faranci Engine                                 | 1/2 |  |  |  |  |

| II         | ı D                   | ECONFIGURABLE SYSTEMS                                                           | 175 |  |  |  |  |

| 11.        | ıN                    | ECONFIGURABLE SISIEMS                                                           | 1/3 |  |  |  |  |

| 9          | Desi                  | gning Pseudo-Reconfigurable Systems                                             | 177 |  |  |  |  |

|            |                       | Why pseudo-reconfigurability?                                                   | 177 |  |  |  |  |

|            |                       | Pros for pseudo-reconfigurability                                               | 177 |  |  |  |  |

|            |                       | Cons for pseudo-reconfigurability                                               |     |  |  |  |  |

|            | 9.1                   | The Pseudo-Reconfigurable Computing System                                      |     |  |  |  |  |

|            | 9.2                   | Kernel Library Concept                                                          |     |  |  |  |  |

|            |                       | 9.2.1 Linear Algebra Kernel Library                                             |     |  |  |  |  |

|            |                       | 7.2.1 Zinem riigeeta richiel Zielah                                             | 1// |  |  |  |  |

| <b>A</b> 1 | nnan                  | dixes                                                                           | 186 |  |  |  |  |

| A          | ppen                  | uixes                                                                           | 100 |  |  |  |  |

| A          |                       | position: the only independent rule in Kleene's model                           | 189 |  |  |  |  |

|            | A.1                   | Preliminary Definitions                                                         | 190 |  |  |  |  |

|            | A.2                   | Primitive Recursion Computed as a Sequence of Compositions                      |     |  |  |  |  |

|            | A.3                   | Minimization Computed as a Sequence of Compositions                             |     |  |  |  |  |

|            | A.4                   | Partial Recursion Means Composition Only                                        |     |  |  |  |  |

| D          |                       | to instantiate DSP48E1                                                          | 195 |  |  |  |  |

| D          | TION                  | W HISTAINIAGE D'ST 40E/1                                                        | 173 |  |  |  |  |

| CONTENTS | (DETAILED) |

|----------|------------|

|          |            |

| C   | Coni   | nexArra | $\mathbf{a}\mathbf{y}^{TM}$ Simulator | 197 |

|-----|--------|---------|---------------------------------------|-----|

|     | C.1    | Top Mo  | odule: simulator.v                    | 97  |

|     | C.2    | Code g  | generator                             | 98  |

|     |        | C.2.1   | Assembly Functions                    |     |

|     |        |         | Add functions                         |     |

|     |        |         | Add with carry functions              |     |

|     |        |         | Bitwise AND functions                 |     |

|     |        |         | Array Control functions               |     |

|     |        |         | Controller's control functions        |     |

|     |        |         | Global functions                      |     |

|     |        |         | Load functions                        |     |

|     |        |         | Multiplication functions              |     |

|     |        |         | Bitwise OR functions                  |     |

|     |        |         | Reverse subtract functions            |     |

|     |        |         | Reverse subtract with carry functions |     |

|     |        |         | Search functions                      |     |

|     |        |         | Shift functions                       |     |

|     |        |         | Store functions                       |     |

|     |        |         | Subtract functions                    |     |

|     |        |         | Subtract with carry functions         |     |

|     |        |         | Transfer functions                    |     |

|     |        |         |                                       |     |

|     |        |         | Bitwise exclusive OR functions        | 115 |

| Bil | bliogr | aphy    | 2                                     | 221 |

# Part I PRELIMINARIES

## **Chapter 1**

## **History**

The history of computation consists of few independent threads, starting in Antiquity. The history starts with an imaginary thread, a conceptual thread and a factual thread. Initially, the concepts and the objects evolved independently. At their mature stage, stimulated by the sad event of World War II, the conceptual evolution interferes with the physical implementation and the IT era begins. Application-driven history gradually emerges around 1971 when the conceptual approach reaches a maturity that slows down the theoretical approaches. In parallel with these threads, along the history, has been manifested and it still manifests also an imaginary thread. One of the main driving force in any domain is the human will and imagination. Therefore, we cannot ignore an ever developing imaginary history of the computing technology and its applications.

#### 1.1 Imaginary history

At the beginning is always an image, a dream.

#### 1.1.1 Antiquity

#### Hephaestus & Vulcan

Greek god Hephaestus is the god of technology, blacksmiths, craftsmen and artisans. Hephaestus made a bronze giant called *Talos* that would patrol around the island and throw rocks at enemy ships.

A roman counterpart of Hephaestus is Vulcan: made slave-girls of gold for himself.

#### **Pygmalion**

Pygmalion was a mythical character who, in search of perfection, sculpted in ivory the image of a perfect woman with whom he later fell in love and the goddess Aphrodite gave life to the statue.

We are always dealing with the human being's aspiration to correct the imperfections of nature through artifacts. Pygmalion seems to be a transhumanist *avant la lettre*.

#### 1.1.2 Middle Ages

There were several stories and legends in the Middle Ages that involved the creation of artificial beings or creatures. These stories often reflected the beliefs and fears of medieval society regarding the power of human beings to create and control life.

#### Golem

Golem (Prague,  $\sim$ 1500) is a metaphor for a brainless entity who serves man under controlled conditions but is hostile to him under others. The earliest known written account of how to create a golem can be found in Jewish Tradition (1165-1230).

#### Artificial animals and creatures at the court of Emperor Frederick II

There were also stories of artificial animals and creatures, such as the legendary mechanical eagle of Holy Roman Emperor Frederick II (1194-1250), which was said to be able to fly and to emit various sounds and cries.

#### **Brazen Head**

Another famous example is the story of the Brazen Head, a mechanical or artificial head that was said to be able to answer any question put to it. According to legend, the head was created by the medieval scholar and philosopher Roger Bacon (1220-1292), who was said to have used his knowledge of natural philosophy to imbue the head with the power of speech and reason.

#### **Homunculus**

Another example is the legend of the Homunculus, a tiny human-like creature that was said to be created by alchemists through the use of special substances and rituals. The Homunculus was believed to possess magical powers and to be able to perform various tasks, including the transmutation of metals and the creation of life. Paracelsus (1493–1541) is credited with the first mention of Homunculus in *De homunculis* (c. 1529–1532), and *De natura rerum* (1537)

Overall, these stories and legends reflected the fascination and curiosity of medieval society with the idea of artificial life and the power of human beings to create and control it.

#### 1.1.3 Modernity

#### Frankenstein's Creature

Mary Shelley (1797-1851, wife of the poet Percy Shelley and daughter of Mary Wollstonecraft a founding figure of feminism) published in 1818 the novel em Frankenstein about a brilliant but unorthodox scientist, Dr. Victor Frankenstein, who rejects the artificial man he created; Creature escapes and later swears revenge.

#### Offenbach's Olympia

Jacques Offenbach (1819-1880) in his *The Tales of Hoffmann* opera finished in 1880 introduced the character *Olympia*, a mechanical or an animatronical doll.

#### Karel Capek's Robota

Robot (*robota* in Russian) is coined by Karel Capek 1920 R.U.R. is a 1920 science fiction play by the Czech writer Karel Čapek. R.U.R. stands for *Rossumovi Univerzální Roboti* (Rossum's Universal Robots). The English phrase "Rossum's Universal Robots" has been used as a subtitle.

#### Fritz Lang's Metropolis

In 1927, German film maker Fritz Lang made the science fiction film Metropolis. The script contains the construction of a robot that acquires perfect human appearance and behavior. The artificial product has the ability to disrupt the behavior of the masses. It's far beyond what was imagined for Capek's robot.

#### 1.1.4 Contemporary

Scary Science Fiction (SF) scenarios about Artificial Intelligence (AI) [Tegmark '17].

Max Tegmark: Life 1.0 referring to biological origins, Life 2.0 referring to cultural developments in humanity, and Life 3.0 referring to the technological age of humans.

We must make distinctions between the three main human brain behaviors: Spiritually – Imaginary – Rationally. AI refers mainly to the third.

#### 1.2 Conceptual history

#### 1.2.1 Binary Arithmetic to the Chinese

In Discourse on the Natural Theology of the Chinese, Gottfried Wilhelm von Leibniz (1646-1716) mentioned that the 64 hexagrams of em I Ching ( $\sim$ 1000 BC) represent the binary arithmetic used a few thousand years ago in China.

#### 1.2.2 Epimenides of Crete

Karl Jaspers (1883–1969) introduced the concept of an Axial Age in his book *The Origin and Goal of History*, published in 1949. During this period new ways of thinking emerged in Persia, India, China, Greece and Roman Empire, in a singular synchronous development, without any effective direct cultural contact between all of the Eurasian cultures. Jaspers emphasized prominent thinkers from this period who had a profound influence on future sciences, philosophies and religions.

In this Axial Age, around 7th or 6th century BC, Epimenides of Cnossos (Crete) was a semi-mythical Greek seer and philosopher-poet which started the conceptual development leading to the contemporary computer science. In one day he uttered a sentence which troubled the inquisitive minds from everywhere for the next two and half millennia:

#### "Cretans, always liars."

The sentence is equivalent with "I lie", and is undecidable: its truth value can not be decided.

#### 1.2.3 Liar's paradox in Middle Ages

In the Middle Ages, the paradox was studied and commented on by many philosophers and theologians, who tried to resolve the contradiction it presents.

#### **Boethius**

Boethius is one of the earliest recorded commentaries on the paradox in the Middle Ages. He is a Roman philosopher who lived in the 6th century CE. In his work "Consolation of Philosophy," Boethius discusses the paradox and argues that it arises from a confusion of terms and concepts.

#### Peter Abelard

6

In the 12th century, the paradox was further discussed by the French philosopher and theologian Peter Abelard, who used it to criticize the doctrine of divine omnipotence. Abelard argued that the paradox shows that there are limits to what even an omnipotent God can do, since he cannot make a statement that is both true and false at the same time.

#### William of Ockham

In the 14th century, the English logician William of Ockham used the paradox to argue against the idea of universal propositions. Ockham argued that the paradox shows that there are no universal propositions that can be true or false in all cases, since there are some statements that cannot be consistently evaluated as true or false.

Overall, the paradox of the liar was a topic of interest and debate among medieval philosophers and theologians, who used it to explore the limits of language, logic, and the nature of truth.

#### 1.2.4 Gottfried Wilhelm von Leibniz

#### **Binary representation**

In 1703, Leibniz published in the *Mémories de l'Académie Royale des Sciences* his essay "Explication de l'arithmétique binaire, qui se sert des seules caractères 0 & 1; avec des remarques sur son utilité, et sur ce qu'elle donne de sens des anciennes figures chinoises de Fohy" where he explains how to perform addition, subtraction, multiplication and division using the binary representation for numbers.

#### Calculus ratiocinator

The *Calculus ratiocinator* is a a concept introduced by Leibniz related to *characteristica universalis*, an universal conceptual language. This concept could be related to both the hardware and software aspects of the modern digital computer.

#### 1.2.5 George Boole

In 1847 George Boole (1815-1864) published *Mathematical Analysis of Logic* and in 1854 *An Investigation into the Laws of Thought, on which are Founded the Mathematical Theories of Logic and Probabilities* which underpins what we now call *Boolean algebra*, a successful attempt to formalize Aristotelian logic. It is thus made available to innovators an instrument that will be used to substantiate the science of calculus as a *decision* tool in the first place, and only through a second approach as a calculation tool. Indeed, computation is mainly about deciding. Numerical computation comes only as a consequence. At first it was the true/false alternative, and only then the 0/1 alternative.

#### 1.2.6 1900-1928: David Hilbert

David Hilbert (1862-1943) one of the most influential and universal mathematicians of the 19th and early 20th centuries.

At the International Congress of Mathematicians held in Bologna, Hilbert revisited to the second of the 23 problems posed in his 1900 paper *Mathematische Probleme* [Hilbert 1900], asking [Isaacson '85]:

1. Was its set of rules complete, so that any statement could be proved (or disproved) using only the rules of the system?

- 2. Was it consistent, so that no statement could be proved true and also proved false?

- 3. Was there some procedure that could determine whether a particular statement was provable, rather than allowing the possibility that some statements (such as enduring math riddles like Fermat's last theorem, Goldbach's conjecture, or the Collatz conjecture) were destined to remain in undecidable limbo?

Hilbert thought that the answer to the first two questions was yes, making the third one moot [Isaacson '85].

In mathematics and computer science, the *Entscheidungsproblem* (German for "decision problem") is a challenge posed by David Hilbert and Wilhelm Ackermann in 1928 [Hilbert & Ackermann '28]. By the completeness theorem of first-order logic, a statement is universally valid if and only if it can be deduced from the axioms, so the Entscheidungsproblem can also be viewed as asking for an algorithm to decide whether a given statement is provable from the axioms using the rules of logic.

As late as 1930, Hilbert believed that there would be no such thing as an unsolvable problem.

The *Entscheidungsproblem* is related to Hilbert's tenth problem (from Hilbert's address of 1900 to the International Congress of Mathematicians in Paris [Hilbert 1900]), which asks for an algorithm to decide whether Diophantine equations have a solution. The non-existence of such an algorithm, established by Yuri Matiyasevich in 1970, also implies a negative answer to the *Entscheidungsproblem*.

Hilbert's address of 1900 to the International Congress of Mathematicians in Paris is perhaps the most influential speech ever given to mathematicians, given by a mathematician, or given about mathematics. In it, Hilbert outlined 23 major mathematical problems to be studied in the coming century.

#### 1.2.7 1931: Kurt Gödel

Kurt Friedrich Gödel (1906-1978) The *logician* Gödel published his two incompleteness theorems in 1931 when he was 25 years old, one year after finishing his doctorate at the University of Vienna. The first incompleteness theorem states that for any self-consistent recursive axiomatic system powerful enough to describe the arithmetic of the natural numbers (for example Peano arithmetic), there are true propositions about the naturals that cannot be proved from the axioms. To prove this theorem, Gödel developed a technique now known as Gödel numbering, which codes formal expressions as natural numbers.

The Austrian-born logician Kurt Gödel polished off **the first two** Hilbert's questions with unexpected answers: no and no. In his "incompleteness theorem", he showed that there existed statements that could be neither proved nor disproved.

#### **1.2.8 1936:** Church – Kleene – Post – Turing

What a synchronicity! Indeed, the logician Gödel's approach triggered four *mathematicians* to provide independently mathematical versions to the logical challenge raised by the *Entscheidungsproblem* (the third of Hilbert's questions).

#### Alonzo Church

Alonzo Church (1903-1995): The lambda calculus emerged in his 1936 paper showing the unsolvability of the *Entscheidungsproblem*. This result preceded Alan Turing's work on the halting problem, which also demonstrated the existence of a problem unsolvable by mechanical means. Church and Turing then showed that the lambda calculus and the Turing machine used in Turing's halting problem were equivalent in capabilities, and subsequently demonstrated a variety of alternative "mechanical processes for computation". This resulted in the Church–Turing thesis.

The lambda calculus influenced the design of the LISP programming language and functional programming languages in general.

#### Stephen Kleene

Stephen Cole Kleene (1909-1994) is best known as a founder of the branch of mathematical logic known as recursion theory, which subsequently helped to provide the foundations of theoretical computer science.

#### **Emil Post**

Emil Leon Post (1897-1957) developed in 1936, independently of Alan Turing, a mathematical model of computation that was essentially equivalent to the Turing machine model. This model is sometimes called "Post's machine" or a Post–Turing machine.

#### **Alan Turing**

"When the great Cambridge math professor Max Newman taught Turing about Hilbert's questions, the way he expressed the *Entscheidungsproblem* was this: Is there a "mechanical process" that can be used to determine whether a particular logical statement is provable?" [Isaacson '85]

Alan Mathison Turing (1912-1954) in 1936 published his paper "On Computable Numbers, with an Application to the *Entscheidungsproblem*". It was published in the Proceedings of the London Mathematical Society journal in two parts, the first on 30 November and the second on 23 December. In this paper, Turing reformulated Kurt Gödel's 1931 results on the limits of proof and computation, replacing Gödel's universal arithmetic-based formal language with the formal and simple hypothetical devices that became known as Turing machines. The *Entscheidungsproblem* (decision problem) was originally posed by German mathematician David Hilbert in 1928. Turing proved that his "universal computing machine" would be capable of performing any conceivable mathematical computation if it were representable as an algorithm. He went on to prove that there was no solution to the decision problem by first showing that the halting problem for Turing machines is undecidable: It is not possible to decide algorithmically whether a Turing machine will ever halt.

#### 1.2.9 1940s: abstract models of computation

The transition from a mathematical model of computation to a realizable physical structure was enabled by the abstract models of computers. Purely mathematical models contain descriptions that assume concepts that have no physical counterpart, such as infinity. For this reason abstract models were necessary.

#### 1943: Neural nets

Warren S. McCulloch, Walter H. Pitts introduced the neural network model for computation [McCulloch '43].

#### 1944: Harvard abstract model

The term originated from the Harvard Mark I, or IBM Automatic Sequence Controlled Calculator (ASCC), an electromechanical computer, which stored instructions on punched tape and data in electromechanical counters.

#### 1945: von Neumann abstract model

John von Neumann wrote up a description titled *First Draft of a Report on the EDVAC* [Neumann '45] based on the work of Eckert and Mauchly. It was unfinished when his colleague Herman Goldstine circulated it, and bore only von Neumann's name (to the consternation of Eckert and Mauchly).

#### 1.3 Factual history

#### 1.3.1 Antikythera mechanism

The Antikythera mechanism is believed to be designed to predict eclipses. It has been designed and constructed by Greeks and is dated to about 200 BC to 80 BC. It is a clockwork mechanism composed of more than 30 engaged bronze gears.

#### 1.3.2 Hero of Alexandria

Hero of Alexandria (c.10-c.70) was the first to build a vending machine; when a coin was introduced via a slot on the top of the machine, a set amount of holy water was dispensed.

Hero described the construction of the aeolipile (a version of which is known as Hero's engine) which was a rocket-like reaction engine and the first-recorded steam engine

#### 1.3.3 Gerbert of Aurillac

In 996 A.D., Gerbert of Aurillac (Pope Sylvester II from 999) (946-1003) invented the first weight-driven mechanical pendulum clock at a monastery in Magdeburg in Germany. The clock's mechanism would ring bells at regular intervals throughout the day to call his fellow monks to prayer.

Gerbert took the idea of the abacus calculator from a Spanish Arab. But the calculations with his abacus were extremely difficult, because the people of his day used only Roman numerals.

#### 1.3.4 Wilhelm Schickard

Johannes Kepler, claimed that the drawings of a calculating clock, predating the public release of Pascal's calculator by twenty years, had been discovered in two unknown letters written by Wilhelm Schickard (1592-1635) to him in 1623 and 1624.

#### 1.3.5 Blaise Pascal

Pascaline: Blaise Pascal (1623-1662) was led to develop a calculator by the laborious arithmetical calculations required by his father's work as the supervisor of taxes in Rouen. He designed the machine to add and subtract two numbers directly and to perform multiplication and division through repeated addition or subtraction.

#### 1.3.6 Gottfried Wilhelm von Leibniz

In Machina arithmetica in qua non additio tantum et subtractio sed et multiplicatio nullo, diviso vero paene nullo animi labore peragantur, written in 1685, Gottfried Wilhelm (von) Leibniz (1646-1716) described an arithmetic machine he had invented that was made by linking two separate machines, one to perform additions/subtractions and one for multiplications/divisions.

#### 1.3.7 Joseph Marie Charles dit Jacquard

The Joseph Jacquard (1752-1834) Loom is a mechanical loom that uses pasteboard cards with punched holes, each card corresponding to one row of the design. Multiple rows of holes are punched in the cards and the many cards that compose the design of the textile are strung together in order.

#### 1.3.8 Charles Babbage

#### Difference engine

Charles Babbage (1791-1871) began in 1822 with what he called the difference engine, made to compute values of polynomial functions. It was created to calculate a series of values automatically. By using the method of finite differences, it was possible to avoid the need for multiplication and division.

#### **Analytical Engine**

The Analytical Engine marks the transition from mechanised arithmetic to fully-fledged general purpose computation. It is largely on it that Babbage's standing as computer pioneer rests.

The major innovation was that the Analytical Engine was to be programmed using punched cards: the Engine was intended to use loops of Jacquard's punched cards to control a mechanical calculator, which could use as input the results of preceding computations.[157][158] The machine was also intended to employ several features subsequently used in modern computers, including sequential control, branching and looping. It would have been the first mechanical device to be, in principle, Turing-complete.

#### 1.3.9 Ada Byron, Countess of Lovelace

Augusta Ada King, Countess of Lovelace (née Byron; 1815–1852) chiefly known for her work on Charles Babbage's proposed mechanical general-purpose computer, the Analytical Engine. She was the first to recognise that the machine had applications beyond pure calculation, and published the first algorithm intended to be carried out by such a machine. As a result, she is sometimes regarded as the first to recognise the full potential of a "computing machine" and one of the first computer programmers.

#### 1.3.10 Herman Hollerith

Herman Hollerith (1860-1929) developed an electromechanical tabulating machine for punched cards to assist in summarizing information and, later, in accounting. His invention of the punched card tabulating machine, patented in 1889, marks the beginning of the era of semiautomatic data processing systems, and his concept dominated that landscape for nearly a century. He was the founder of the Tabulating Machine Company that was amalgamated (via stock acquisition) in 1911 with three other companies to form a fifth company, the Computing-Tabulating-Recording Company, which was renamed IBM in 1924. Hollerith is regarded as one of the seminal figures in the development of data processing.

#### 1.3.11 Claude Shannon & Thomas Flowers

#### Implementing electro-mechanically Boolean functions

Claude Elwood Shannon (1916-2001) known as "the father of information theory". Shannon is noted for having founded information theory with a landmark paper, *A Mathematical Theory of Communication*, that he published in 1948.

He is also well known for founding digital circuit design theory in 1937, when — as a 21-year-old master's degree student at the Massachusetts Institute of Technology (MIT) — he wrote his thesis demonstrating that electrical applications of Boolean algebra could construct any logical numerical relationship.

#### **Implementing electronically Boolean functions**

Thomas Harold Flowers (1905-1998). From 1935 onward, he explored the use of electronics for telephone exchanges and by 1939, he was convinced that an all-electronic system was possible. A background in switching electronics would prove crucial for his computer designs [Copeland '06].

11

#### 1.4 Merged history

The triad *Math & Logic – War – Technology* (Ethos – Pathos – Logos) provides the context of the emergence of the Information Technology (IT) era.

WWII made the turbulent transition toward IT industry.

#### 1.4.1 Colossus

Colossus was a set of computers developed by British code-breakers in the years 1943–1945 to help in the cryptanalysis of the Lorenz cipher. Colossus used thermionic valves (vacuum tubes) to perform Boolean and counting operations. Colossus is thus regarded as the world's first programmable, electronic, digital computer, although it was programmed by switches and plugs and not by a stored program.

A Colossus computer was thus not a fully Turing complete machine. The notion of a computer as a general purpose machine — that is, as more than a calculator devoted to solving difficult but specific problems — did not become prominent until after World War II.

#### 1.4.2 ENIAC – EDVAC

#### **ENIAC**

Electronic Numerical Integrator and Computer was the first electronic general-purpose computer. It was Turing-complete, digital and able to solve "a large class of numerical problems" through reprogramming. ENIAC was completed in 1945 and first put to work for practical purposes on December 10, 1945.

ENIAC was designed by *John Mauchly* and *J. Presper Eckert* of the University of Pennsylvania, U.S.

By the end of its operation in 1956, ENIAC contained 20,000 vacuum tubes; 7,200 crystal diodes; 1,500 relays; 70,000 resistors; 10,000 capacitors; and approximately 5,000,000 hand-soldered joints. It weighed more than 27 t, was roughly  $2.4m \times 0.9m \times 30m$  in size, occupied  $167m^2$  and consumed 150kW of electricity.

#### **EDVAC**

Electronic Discrete Variable Automatic Computer: unlike its predecessor, the ENIAC, it was binary rather than decimal, and was designed to be a stored-program computer. Functionally, EDVAC was a binary serial computer with automatic addition, subtraction, multiplication, programmed division and automatic checking with an ultrasonic serial memory[1] capacity of 1,000 34-bit words. EDVAC's average addition time was 864 microseconds and its average multiplication time was 2,900 microseconds.

ENIAC inventors John Mauchly and J. Presper Eckert proposed EDVAC's construction in August 1944, and design work for EDVAC commenced before ENIAC was fully operational. The design would implement a number of important architectural and logical improvements conceived during the ENIAC's construction and would incorporate a high-speed serial-access memory. Like the ENIAC, the EDVAC was built for the U.S. Army's Ballistics Research Laboratory at the Aberdeen Proving Ground by the University of Pennsylvania's Moore School of Electrical Engineering. Eckert and Mauchly and the other ENIAC designers were joined by John von Neumann in a consulting role; von Neumann summarized and discussed logical design developments in the 1945 First Draft of a Report on the EDVAC.

12 CHAPTER 1. HISTORY

#### 1.4.3 Princeton computer

The IAS machine was the first electronic computer to be built at the Institute for Advanced Study (IAS) in Princeton, New Jersey. It is sometimes called the von Neumann machine, since the paper describing its design was edited by John von Neumann, a mathematics professor at both Princeton University and IAS. The computer was built from late 1945 until 1951 under his direction.

The IAS machine was a binary computer with a 40-bit word, storing two 20-bit instructions in each word. The memory was 1,024 words (5.1 kilobytes). Negative numbers were represented in "two's complement" format. It had two general-purpose registers available: the Accumulator (AC) and Multiplier/Quotient (MQ). It used 1,700 vacuum tubes. The memory was originally designed for about 2,300 RCA Selectron vacuum tubes.

It weighed about 1,000 pounds (450 kg).[11]

It was an asynchronous machine, meaning that there was no central clock regulating the timing of the instructions. One instruction started executing when the previous one finished. The addition time was 62 microseconds and the multiplication time was 713 microseconds.

#### 1.4.4 IBM entered the scene

The IBM 701 Electronic Data Processing Machine, known as the Defense Calculator while in development, was IBM's first commercial scientific computer, which was announced to the public on April 29, 1952. It was designed by Nathaniel Rochester and based on the IAS machine at Princeton.

#### 1.4.5 John Backus: first involvement

John Warner Backus (1924-2007): directed the team that invented and implemented FORTRAN, the first widely used high-level programming language, and was the inventor of the Backus–Naur form (BNF), a widely used notation to define formal language syntax.

#### 1.4.6 Computer architecture

Brooks went on to help develop the IBM System/360 (now called the IBM zSeries) line of computers, in which "architecture" became a noun defining "what the user needs to know".

In [Amdahl '64] [Blaauw '64] the concept of computer architecture (low level machine model) is introduced to allow independent evolution for the two different aspects of computer design, which have different rate of evolution: software and hardware; thus, there are now on the market few stable and successful architectures, such as x86, ARM, PowerPC.

#### 1.4.7 John Backus: second involvement

He later did research into the function-level programming paradigm, presenting his findings in his influential 1977 Turing Award lecture "Can Programming Be Liberated from the von Neumann Style? A Functional Style and Its Algebra of Programs"

#### 1.4.8 Parallel computing enter the scene on the back door

While for mono-core computing there are the following stages [?]:

• 1936 – mathematical computational models: four equivalent models are published [Turing '36] [Church '36] [Kleene '36] [Post '36] (all reprinted in [Davis '04]), out of which the *Turing Machine* offered the most expressive and technologically appropriate suggestion for future developments leading eventually to the mono-core, sequential computing

- **1944-45 abstract machine models**: the MARK 1 computer, built by IBM for Harvard University, consecrated the *Harvard abstract model*, while the von Neumann's report [Neumann '45] introduced the *von Neumann abstract model*; these two concepts backed the *RAM* (random access machine) abstract model used to evaluate algorithms for sequential machines

- 1952 manufacturing in quantity: IBM launched *IBM 701*, the first large-scale electronic computer

- late 1953 high-level programming language: John W. Backus submitted a proposal to his superiors at IBM to develop a more practical alternative to assembly language for programming their IBM 704 mainframe computer; a draft specification for "The IBM Mathematical Formula Translating System" was completed by November 1954; the first manual for FORTRAN appeared in October 1956; with the first FORTRAN compiler delivered in April 1957.

- **1964 computer architecture**: in [Blaauw '64] the concept of *computer architecture* (low level machine model) is introduced to allow the independent development for the two different aspects of computer design which have different rate of evolution: software and hardware; thus, there are now on the market few stable and successful architectures, such as x86, ARM, ....

for parallel computing we are faced with a completely distorted evolution; let us see its first stages:

- 1962 manufacturing in quantity: the first symmetrical MIMD engine is introduced on the computer market by Burroughs

- 1965 architectural issues: Edsger W. Dijkstra formulates in [Dijkstra '65] the first concerns about specific parallel programming issues

- 1974-76 abstract machine models: proposals of the first abstract models (bit vector models in [Pratt '74] and PRAM models in [Fortune '78], [Goldschlager '82]) start to come in after almost two decades of non-systematic experiments (started in the late 1950) and the too early market production

- ? mathematical computation model: no one yet really considered it, regrettably confused with abstract machine models, although it is there waiting for us (see Kleene's mathematical model for computation [Kleene '36]).

#### 1.4.9 **RISC**

The term RISC (Reduction Instruction Set Computer) was coined by David Patterson. It means processors with an architecture characterized by:

- **load-store mechanism**: divides instructions into two categories: ALU operations between registers, and memory access as simple load and store between memory and registers instead complex multi-indirected memory access modes

- **one-word instructions**: instructions are coded in on word; even when an immediate value is involved, it is taken into account that in most cases small values are involved that can be encoded with a small number of bits making it unnecessary to add an additional word to specify the value.

- **one-cycle execution**: using a Harvard abstract model, a load-store mechanism and one-word instructions, it is possible to design a processor which execute each instruction in one clock cycle

- **only most frequent instructions**: because the statistics compiled on large program databases showed an uneven distribution of the use of the instructions in the established ISAs, it was decided to keep in the ISA only the frequently used instructions, provided that the omitted ones could be made by a sequence of those maintained

14 CHAPTER 1. HISTORY

which will lead to:

The goal of any instruction format should be: 1. simple decode, 2. simple decode, and 3. simple decode. Any attempts at improved code density at the expense of CPU performance should be ridiculed at every opportunity. [Weaver '09]

The resulting reductions in complexity and size have increased the number of registers, increased clock frequency and reduced power consumption.

The first implementations:

- **IBM 801**: based on a statistical study launched in the mid-1970s that highlighted the need to increase the number of registries and the possibility of removing from current ISAs a significant number of complex instructions that compilers "ignored".

- **Berkeley RISC**: when David Patterson was sent in 1979 on a sabbatical from University of California, Berkeley to help DEC to improve the VAX microcode, he discovered that if the microcode was removed, the programs would run faster. The microcode was responsible for interpreting the complex instructions. Then, removing the complex instructions from ISA becomes a solution for improving processor's performance.

- **MIPS**: stands for Microprocessor without Interlocked Pipeline Stages, a project which came from a graduate course of John L. Hennessy At Stanfort University; it produced a functioning system in 1983.

Since 2010 a new *open source* ISA, RISC-V, has been under development at the University of California, Berkeley.

#### 1.4.10 FPGA & Adaptive Computer Acceleration Platform

1985 is considered the year of the birth of FPGA (Field-Programmable Gate Array) technology with the founding of Xilinx, although in 1983 the founding of Altera led to the first forms of this technology.

ACAP (Adaptive Computer Acceleration Platform) is the technology that naturally emerges from the FPGA approach by the fact that users of the last decades have expressed preferences that have outlined specific structures that can be implemented as standardizable IPs.

An ACAP is a heterogeneous, hardware adaptable platform that is built from the ground up to be fully software programmable. An ACAP is fundamentally different from any multi-core architecture in that it provides hardware programmability but the developer does not have to understand any of the hardware detail. [Banerjee '19]

## 1.5 User-driven evolution: Computation as General-Purpose Technology

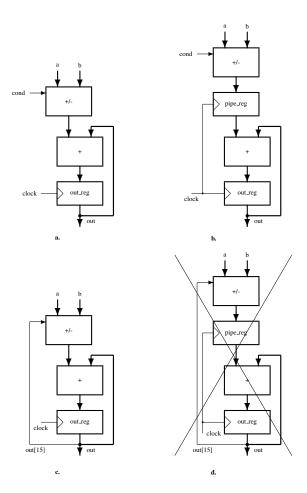

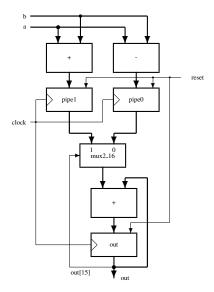

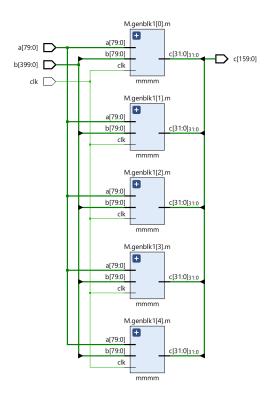

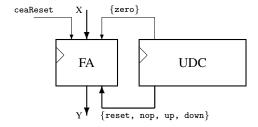

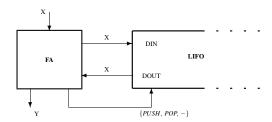

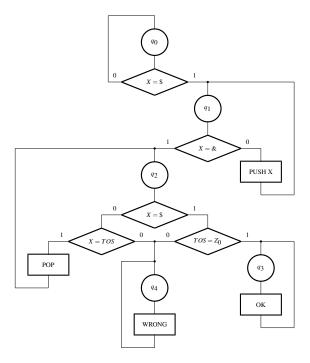

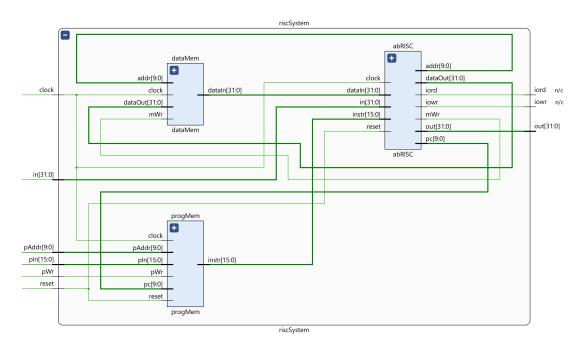

#### 1.5.1 Microsoft's Surface